## Solutions - Quiz 1

(January 23<sup>rd</sup> @ 5:30 pm)

## PROBLEM 1 (40 PTS)

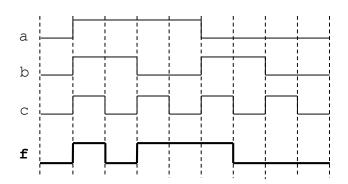

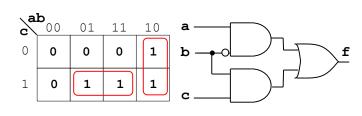

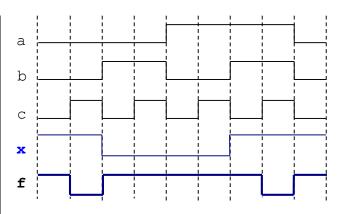

The following is the timing diagram of a logic circuit with three inputs. Simplify the Boolean expression of the circuit and sketch the minimized circuit.

$$f = bc + a\overline{b}$$

## **PROBLEM 2 (30 PTS)**

• Complete the timing diagram of the logic circuit whose VHDL description is shown below:

```

library ieee;

use ieee.std logic 1164.all;

entity test is

port (a, b, c: in std logic;

f: out std logic);

end test;

architecture struct of test is

signal x: std logic;

begin

f <= x nand c;

x \le a \times b;

end struct;

```

## **PROBLEM 3 (30 PTS)**

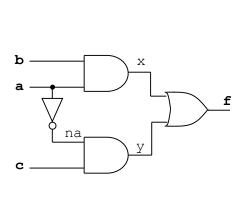

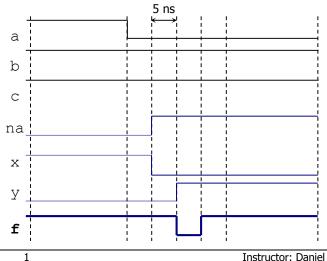

• Complete the timing diagram of the digital circuit shown below. You must consider the propagation delays. Assume the propagation delay of every gate is 5 ns. The initial values of all signals are plotted in the figure.